# SBR Technology

「6G時代の幕開け」～クラウドからエッジへ拡張するフィジカルAIを

支えるチッププレットパッケージと光電融合～

(@第40回ネプコンジャパン- プリント配線板EXPO)

2026年1月21日 説明版

株式会社SBRテクノロジー

西尾俊彦

Copyright©2025, SBR Technology Co., Ltd, All rights reserved.

- フィジカルAI x ローカル6G x MEC x デジタルツイン

- チッププレットパッケージのトレンド

- 光電融合パッケージのトレンド

- まとめ

- フィジカルAI x ローカル6G x MEC x デジタルツイン

- チップレットパッケージのトレンド

- 光電融合パッケージのトレンド

- まとめ

# フィジカルAI x ローカル6G x デジタルツイン

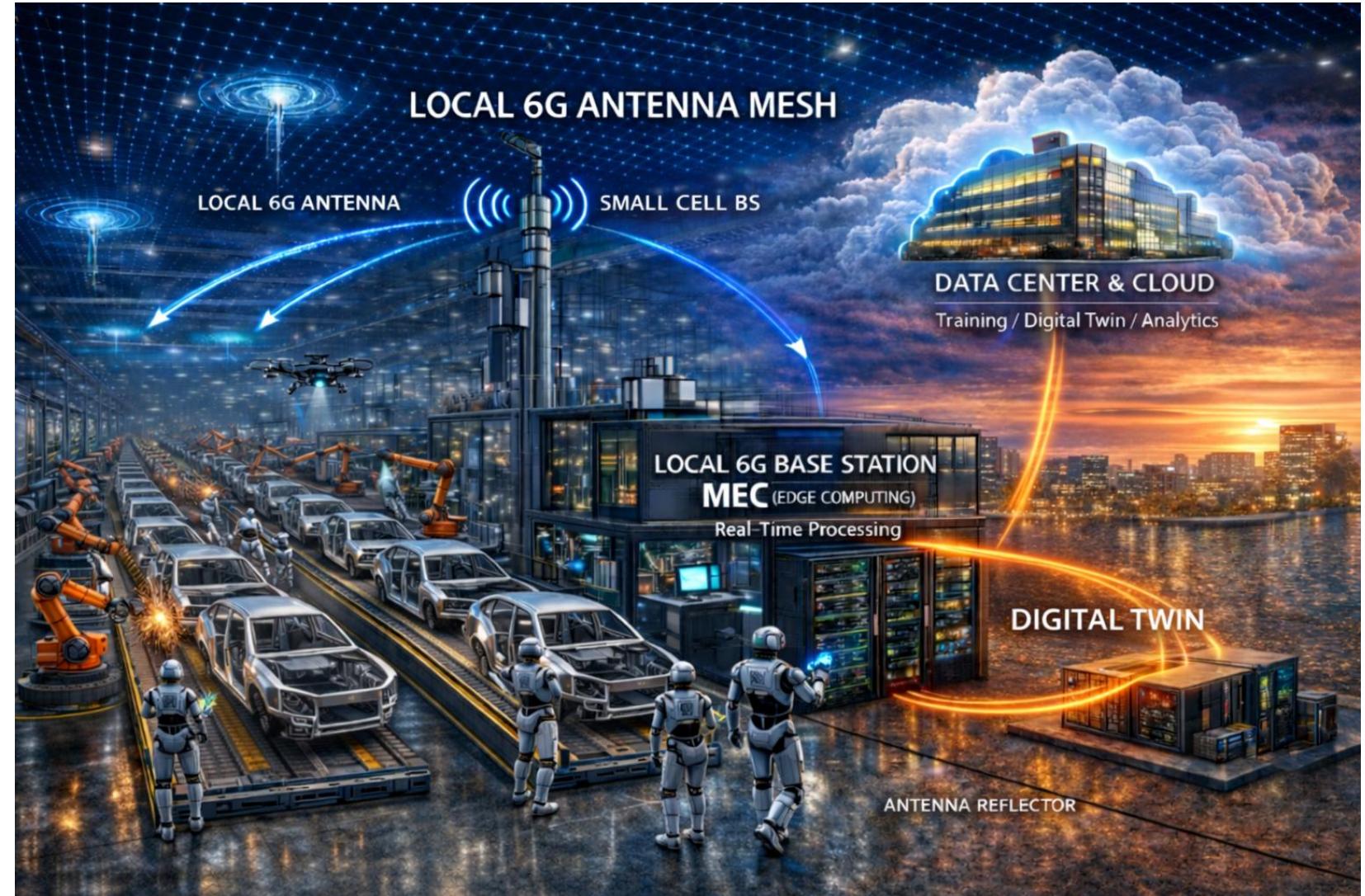

PHYSICAL AIとは、AIがデジタル空間で判断するだけでなく、現実世界（物理空間）で「感じて・考えて・動く」ことを前提に設計されたAIです。

MEC(Multi-access Edge Computing):クラウドの計算機能やAI処理を、ユーザーや機器の近く（通信ネットワークのエッジ）に配置する仕組みです。

Local 6Gとは、6G技術を公衆網ではなく、工場・倉庫・港湾・病院・キャンパスなどの限定エリアで専用利用する通信方式です。

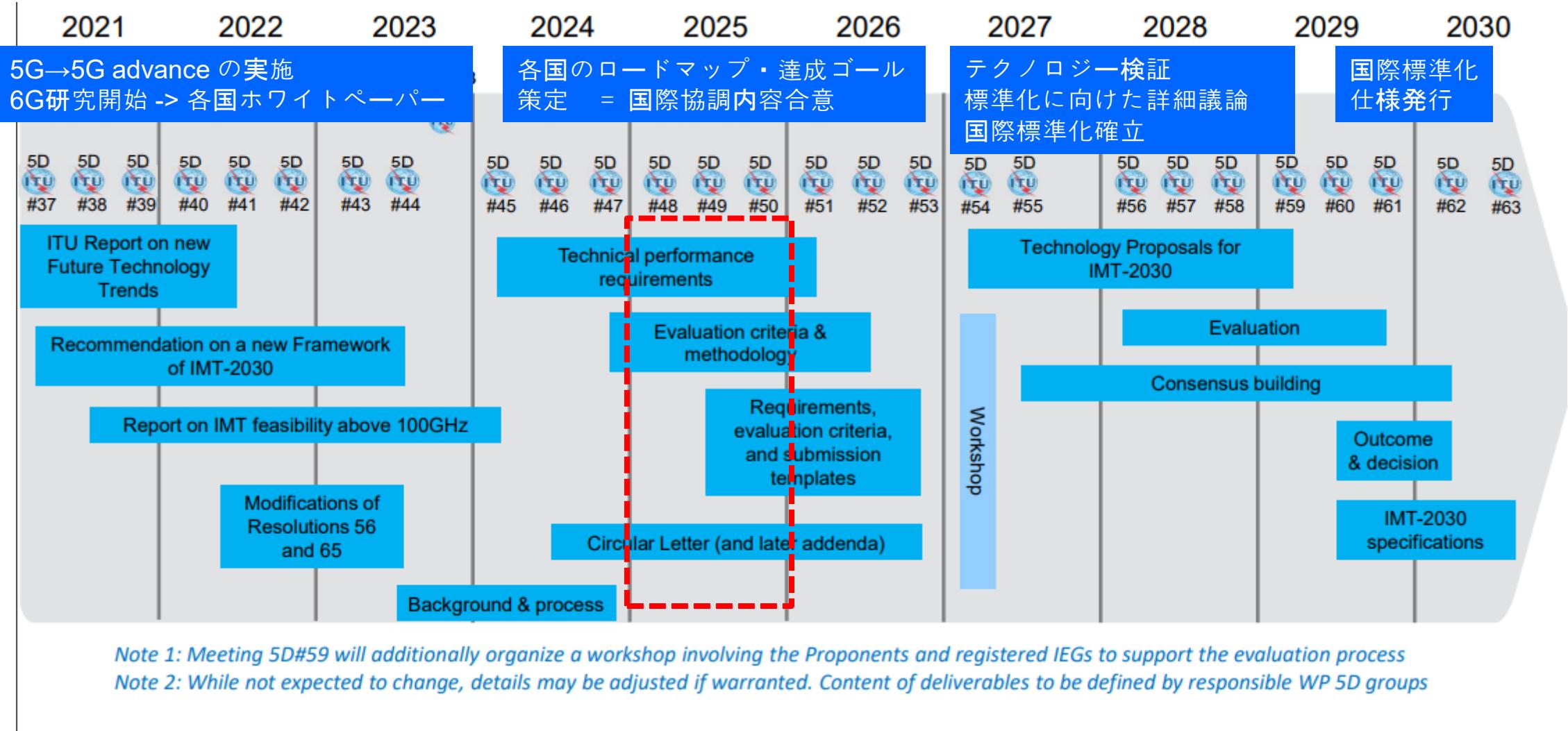

# ITU(国際電気通信連合) 6G仕様制定までのマイルストーン -

# 提案されている各国の6G周波数帯(2025年時点)

| Region        | FR1 / Sub-10 GHz | mmWave    | Sub-THz     | Policy Emphasis                        |

|---------------|------------------|-----------|-------------|----------------------------------------|

| United States | 7-16 GHz         | 24-71 GHz | 95-325 GHz  | Technology-first, early Sub-THz access |

| Japan         | 7-15 GHz         | 26-90 GHz | 100-300 GHz | Practical deployment, coexistence      |

| China         | 6-15 GHz         | 24-52 GHz | 92-300 GHz  | State-driven, aggressive Sub-THz       |

| Europe (EU)   | 7-20 GHz         | 26-70 GHz | 100-300 GHz | Harmonization, industrial focus        |

United States (2025):• FCC, 6G Notice of Inquiry (2024–2025) ( <https://www.fcc.gov/document/fcc-launches-inquiry-toward-next-generation-6g-wireless> )

Japan (2025):• MIC, Beyond 5G / 6G Promotion Strategy 2.0 (2025) ( [https://www.soumu.go.jp/main\\_sosiki/joho\\_tsusin/eng/beyond5g.html](https://www.soumu.go.jp/main_sosiki/joho_tsusin/eng/beyond5g.html) )

China (2025):• IMT-2030 (6G) Promotion Group White Paper (2025) ( <http://www.imt-2030.org.cn/> )

Europe (EU, 2025):• RSPG, 6G Spectrum Roadmap (2025) ( <https://radio-spectrum-policy-group.ec.europa.eu/> )

Global:• ITU-R, IMT-2030 Framework (2024–2025) ( <https://www.itu.int/en/ITU-R/study-groups/rsg5/rwp5d/Pages/imt-2030.aspx> )

- フィジカルAI x ローカル6G x デジタルツイン

- チッププレットパッケージのトレンド

- 光電融合パッケージのトレンド

- Q&A

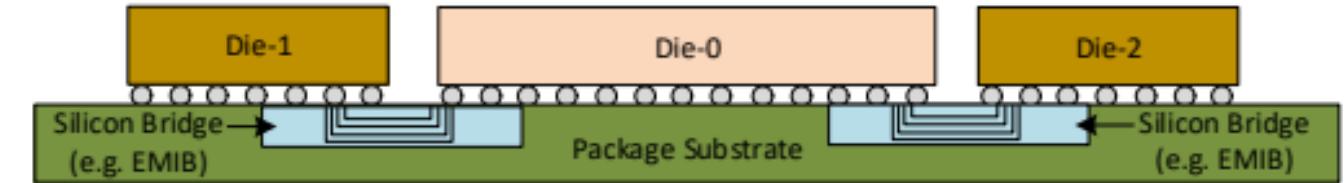

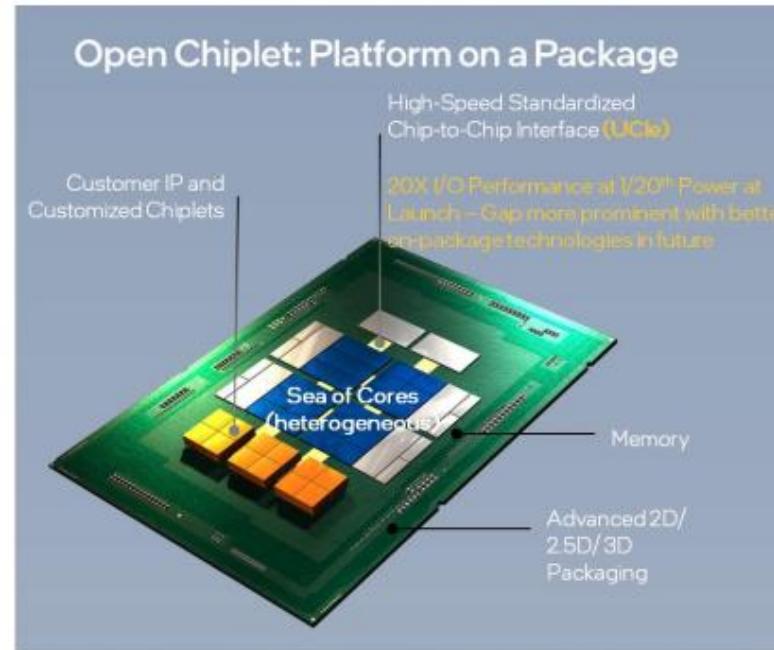

# チップレットとは (UClE定義)

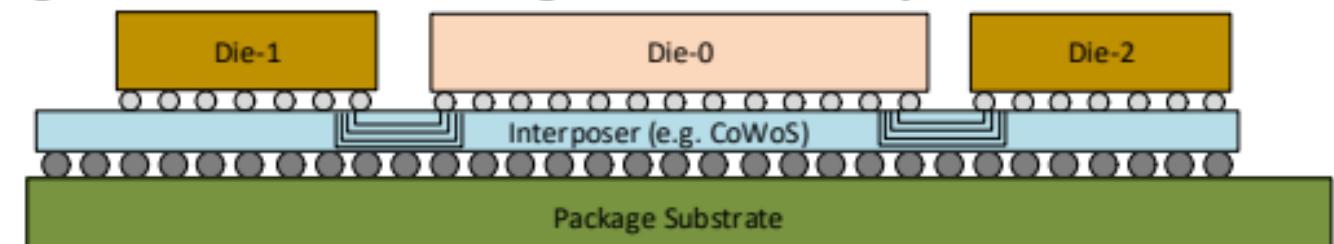

Figure 5. Advanced Package interface: Example 2

Figure 6. Advanced Package interface: Example 3

Figure 4. Advanced Package interface: Example 1

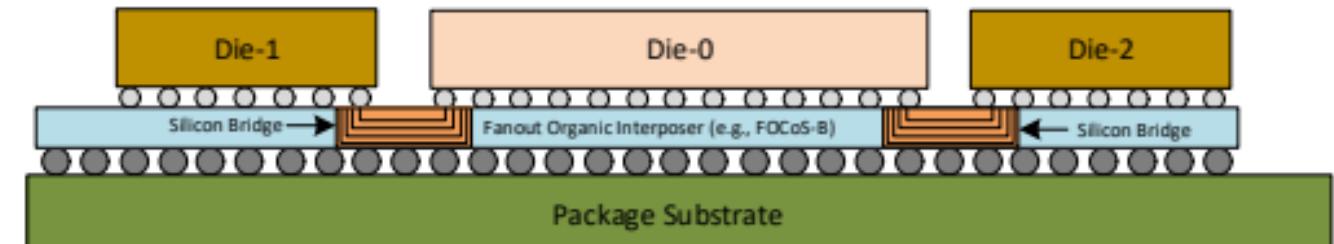

Figure 1. A Package comprising of CPU dies, Accelerator die(s), and I/O Tile die connected through UClE

# チップレットアプリケーション

| Applications        | Chiplets types                      |

|---------------------|-------------------------------------|

| Cloud AI Training   | FO-bridge interposer                |

| Cloud AI inference  | Silicon interposer (RDL interposer) |

| Cloud CPU           | RDL interposer<br>EMIB              |

| Cloud SW (Router)   | RDL interpose<br>Silicon interposer |

| Enterprise AI       | Silicon interposer (RDL interposer) |

| MEC/Base Station AI | RDL interpose                       |

| PC desktop / AI     | RDL interposer                      |

| PC note / AI        | RDL interposer                      |

| Automotive          | RDL interposer                      |

| Gaming/Industrial   | RDL interposer                      |

Cloud servers

High performance

Scal out

Networks

High speed

High capacity

Edge devices

High RF performance

Integrated form factor

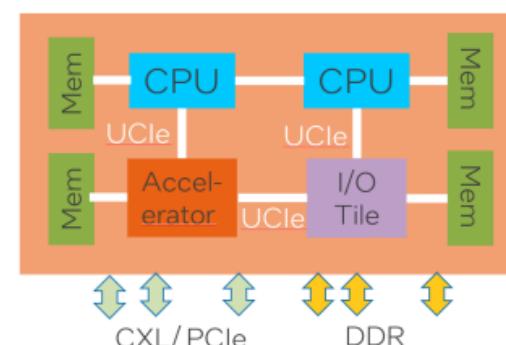

Cloud AI = AI training cluster / Inference service servers /

## Generative AI

400GbE -> 1.6TbE

Enterprise AI = Security / Research & Development / Local AI cluster

High efficiency

And optimized backhaul

5G -> 6G

400GbE -> 1.6TbE

5G -> 6G

Virtual Model Simulation

Real

Smart factory

Smart city

Autonomous driving

V2X connections

Edge / Local AI = Security / Low latency / Safety

# 典型的なチップレットアーキテクチャ(AIユースケース)

| System Level             | Primary Use Case                        | Typical Chiplet Composition                  | Interconnect             | Packaging                  | Representative Examples          |

|--------------------------|-----------------------------------------|----------------------------------------------|--------------------------|----------------------------|----------------------------------|

| DC AI Server             | LLM Training / Large Inference          | GPU Compute Die × N, HBM Stacks × M, I/O Die | NVLink / Infinity Fabric | 2.5D / 3D (CoWoS)          | AMD MI300, NVIDIA B200           |

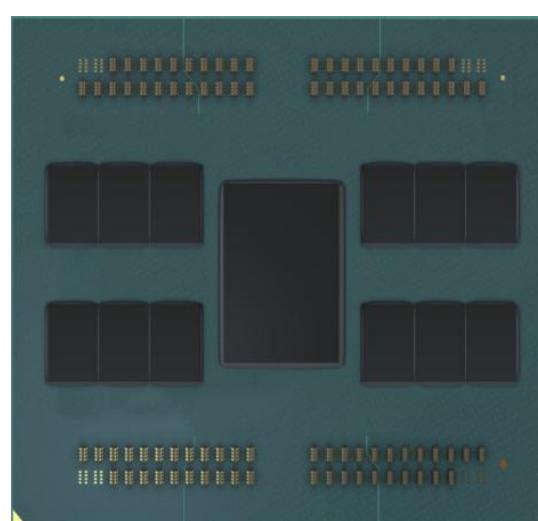

| CPU Server               | Inference, Control, Pre/Post Processing | CPU Core Die × 8-12, I/O Die                 | Infinity Fabric          | 2.5D Organic Substrate     | AMD EPYC (Genoa / Turin)         |

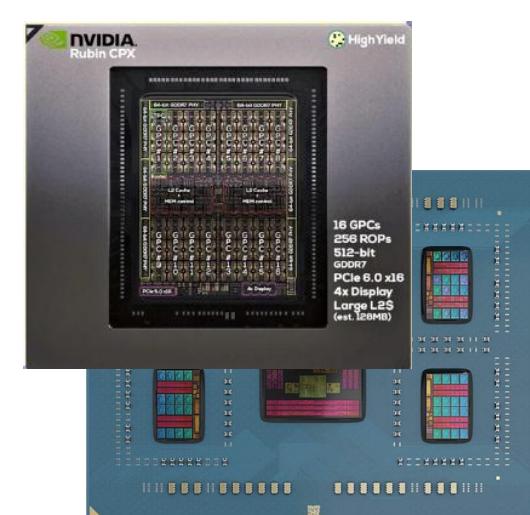

| MEC Server               | Edge AI, Low-Latency Control            | CPU Core Die × 2-4, AI Accel Die, I/O Die    | Infinity Fabric / UClie  | Compact 2.5D               | AMD EPYC 8004, Nvidia Rubin CPX  |

| Walking Robot / Embedded | Perception, SLAM, Motion Control        | CPU Die, GPU Die, NPU Die (small)            | On-die Fabric            | Monolithic / Light Chiplet | AMD Ryzen 8000, Nvidia Rubin CPX |

- AMD MI300 Chiplet Architectur: <https://www.amd.com/en/products/accelerators/instinct/mi300>

- NVIDIA Blackwell / B200 Platform: <https://www.nvidia.com/en-us/data-center/blackwell/>

- AMD EPYC Chiplet Design (Genoa / Turin): <https://www.amd.com/en/processors/epyc>

- AMD EPYC 8004 (Siena) for Edge Servers: <https://www.amd.com/en/products/processors/server/epyc/8004-series>

- AMD Ryzen Embedded 8000 Series: <https://www.amd.com/en/products/embedded/ryzen-embedded-8000-series>

# 典型的なチップレットアーキテクチャ(AIユースケース)

| Category                    | DC AI Server                                                   | CPU Server                            | MEC AI Server                                                   | Walking Robot / Embedded                           |

|-----------------------------|----------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------|----------------------------------------------------|

| System Level                | DC AI                                                          | DC CPU                                | Edge / MEC                                                      | Edge / Robot                                       |

| Typical Chiplet Composition | GPU Compute Die $\times$ N<br>HBM Stacks $\times$ M<br>I/O Die | CPU Core Die $\times$ 8-12<br>I/O Die | CPU Core Die $\times$ 2-4<br>(Optional AI Accel Die)<br>I/O Die | CPU + GPU + NPU Die<br>(small)                     |

| Packaging                   | 2.5D / 3D (CoWoS)                                              | 2.5D Organic Substrate                | Compact 2.5D / FC-BGA                                           | Compact 2.5D / FC-BGA                              |

| Representative Examples     | AMD MI300<br>NVIDIA B200                                       | AMD EPYC<br>(Genoa / Turin)           | AMD EPYC 8004<br>+ Nvidia Rubin CPX                             | AMD Ryzen Embedded 8000<br>+ Tenstorrent Garyskull |

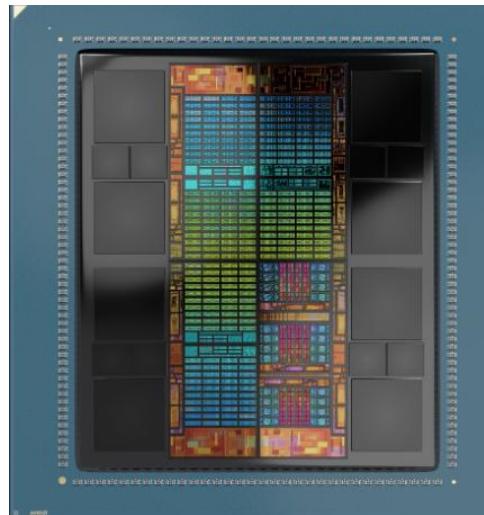

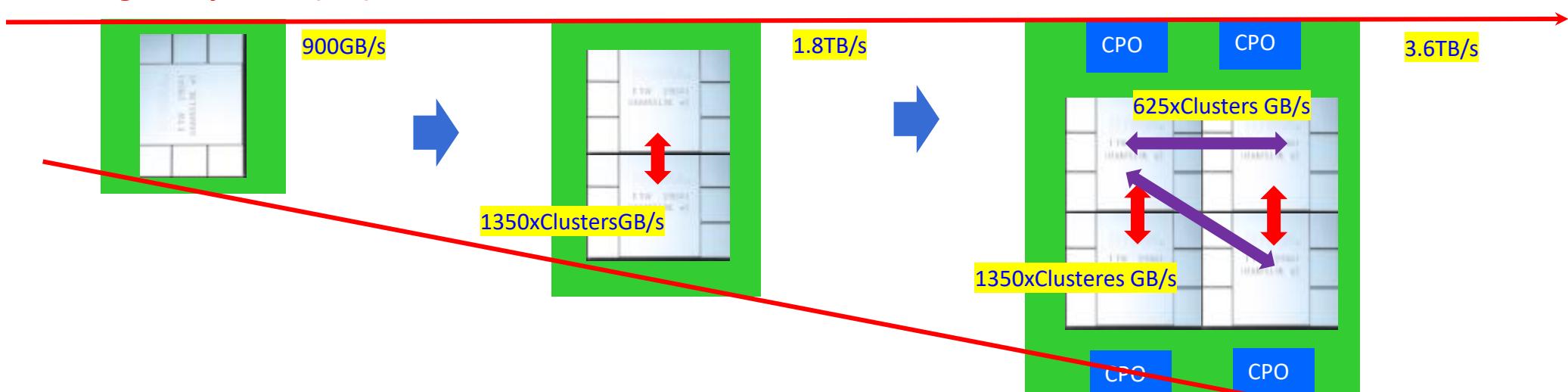

# 学習モデルトレーニング用チップレットトレンド

2 Reticle RDL Interposer

1 die on the interposer

900GB/s<sup>\*1</sup> – Package to Package

3 directions: 2700GB/s

**Base bandwidth**

55 x 55 mm (1.0)<sup>\*4</sup>

7-2-7<sup>\*4</sup>

Df < 0.004<sup>\*4</sup>

Plating area yielded (1.0)

4 Reticle ABFO

2 dies on the interposer

24750 GB/s<sup>\*2</sup> – Die to Die with the bridge

900GB/s<sup>\*1</sup> – Package to Package

3 directions: 23400 GB/s

**8.7 times bandwidth**

85 x 85 mm (x1.7)<sup>\*4</sup>

9 -2 -9<sup>\*4</sup>

Df < 0.003<sup>\*4</sup>

Plating area yielded (x2.4)

8 Reticle interposer by ABFO

4 dies on the interposer

27450 GB/s<sup>\*2</sup> – Die to Die with the bridge

172800 GB/s<sup>\*3</sup> – Die to Die with RDL

3 directions: 43200 GB/s

**16 times bandwidth**

>100 x 120mm (x2.8)<sup>\*4</sup>

11 -2 -11<sup>\*4</sup>

Df < 0.002<sup>\*4</sup>

Plating area (x5.5)

\*1: NVLink gen 4.0

\*2: UCIe: 1350GB/s/mm<sup>2</sup>/cluster(64bits) x 16 clusters

\*3: UCIe: 625GB/s/mm/cluster(64bits) x 16 clusters

\*4: Typical specifications for examples

# チップレットパッケージの材料と信頼性課題

材料はほとんどの種類について日本勢が上位シェアでほぼ独占

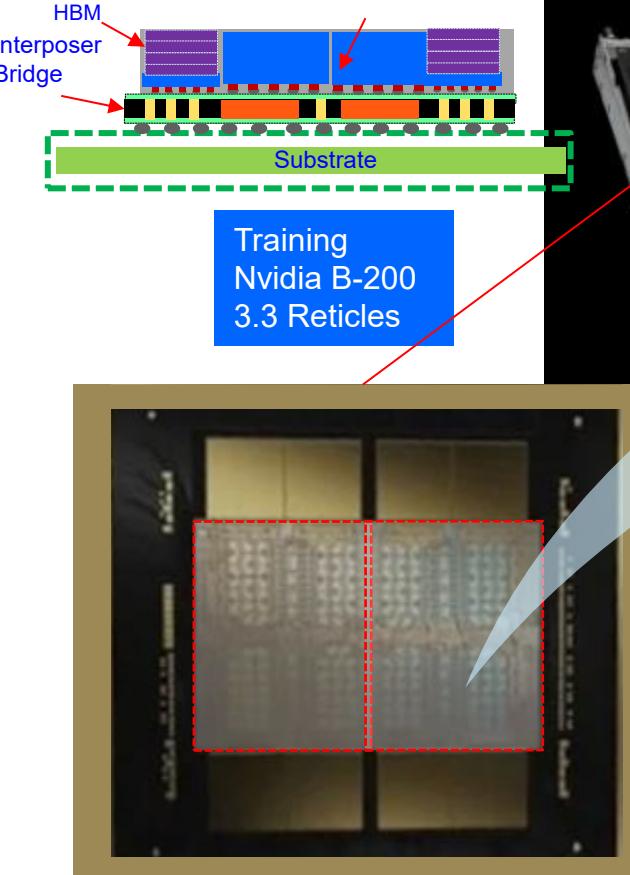

シリコンインターポーザーは3.3Rが限界だが、最も適用実績が長い（2012年から量産）

ファンアウトインターポーザーは有機材料の寸法・品質制御が課題（2024年からの量産）

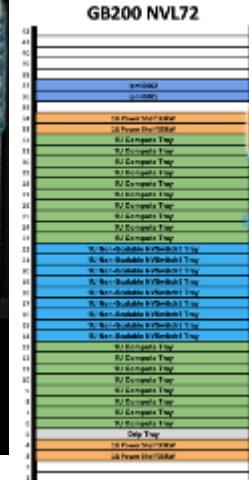

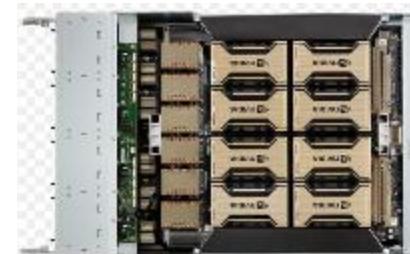

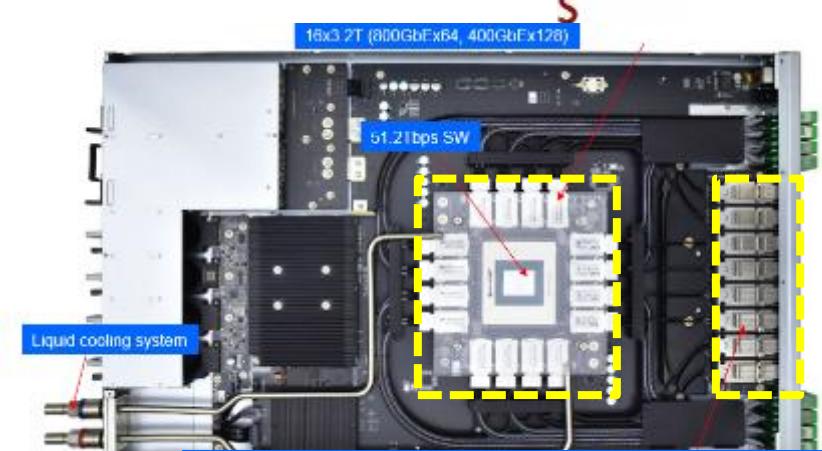

# Nvidia NVLサーバー - Supper Pod

Training

GB200 Server

B200 (AI) x 2

+ Grace (CPU)

Nvlinkで接続できる

Clusterは576GPGPU

となり、H100 世代の

256の倍以上になりより

効率的なネットワーク接続が実現

Training

GB200 NVL72

Rack server

B200 (AI) x 72

+ Grace (CPU) x 36

|                                            | NVIDIA H100 | NVIDIA B200 |

|--------------------------------------------|-------------|-------------|

| Package Size (mm) (est.)                   | 55x55       | 70 × 70     |

| Chiplets Size (Interposer) Reticles (est.) | 2           | 3.3         |

| HBM Capacity (GB)                          | 80 (HBM3)   | 192 (HBM3e) |

| HBM Bandwidth (TB/s)                       | 3.35T       | 8T          |

| INT8 FLOPS (TFLOPS)                        | 2000        | 3000        |

| TDP (W)                                    | - 700       | - 1200      |

Nvidiaなど発表記事よりSBRテクノロジー作成

- 2025年からハイパースケーラーに対して納入が始まるのは BVLサーバー。

- B200x2とGraceを搭載したマザーボードX のサーバーをX18 とした最小ラック構成。

- このラックをX xK個接続したトレーニングシステム。

# フィジカルAI x ローカル6G x デジタルツイン

PHYSICAL AIとは、AIがデジタル空間で判断するだけでなく、現実世界（物理空間）で「感じて・考えて・動く」ことを前提に設計されたAIです。

MEC(Multi-access Edge Computing):クラウドの計算機能やAI処理を、ユーザーや機器の近く（通信ネットワークのエッジ）に配置する仕組みです。

Local 6Gとは、6G技術を公衆網ではなく、工場・倉庫・港湾・病院・キャンパスなどの限定エリアで専用利用する通信方式です。

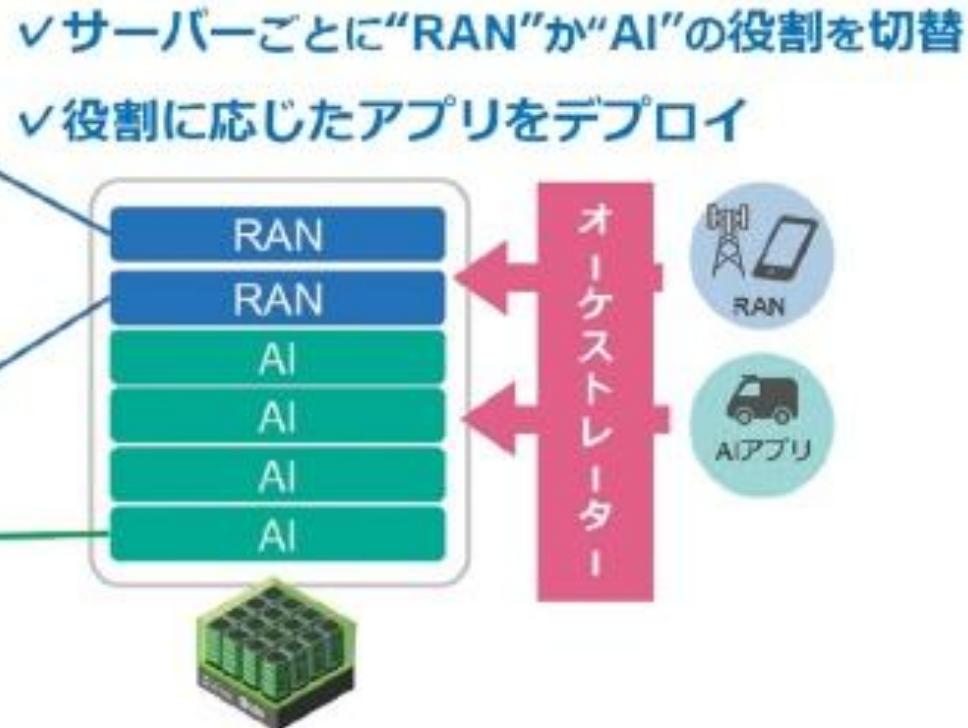

図5 オーケストレーターが役割を分担

オーケストレーターが、AIとRANそれぞれのアプリケーションの特性を踏まえて効率的にコンピューティングリソースを動的に配分する。1台のサーバーにAIとRANの両方のワークロードを割り当てることも可能（出所：ソフトバンク）

<https://xtech.nikkei.com/atcl/nxt/mag/ne/18/00123/00003/>

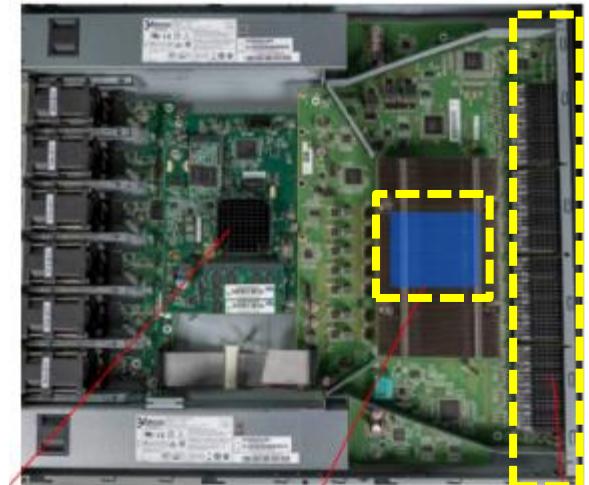

**AMD**

**EPYC**

Processor: (1) Socket SP6

Rackmount: 1U

Storage Bay: 12 SFF

PSU: 1+1 CRPS

Others: Up to 12 NVMe U.2; 12 DIMM; 2 PCIe 5.0 x16

Segment: Cloud Computing

[https://www.mitaccomputing.com/jp/page/amd\\_epyc\\_8004](https://www.mitaccomputing.com/jp/page/amd_epyc_8004)

- フィジカルAI x ローカル6G x デジタルツイン

- チッププレットパッケージのトレンド

- 光電融合パッケージのトレンド

- まとめ

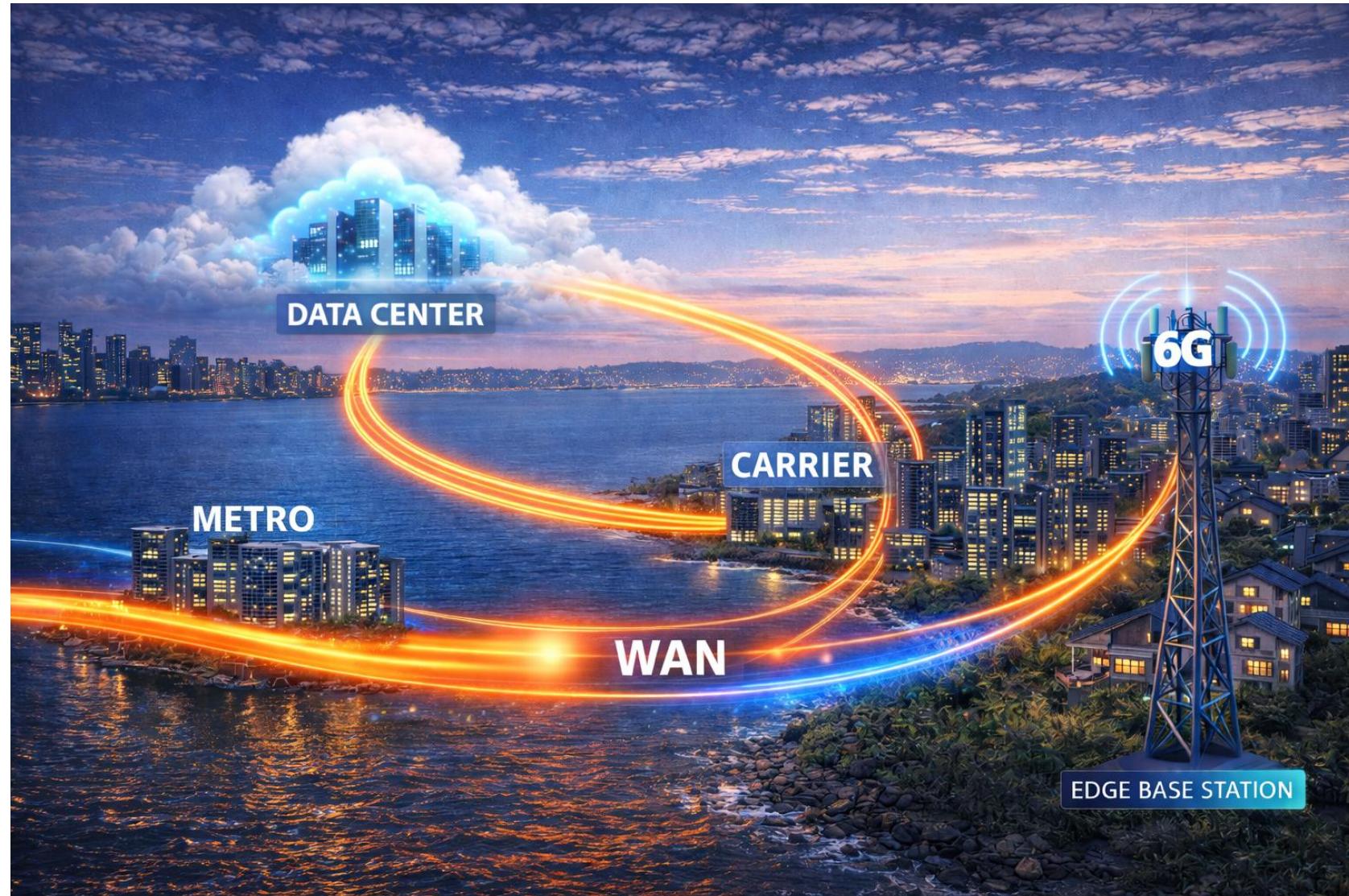

# 超高速光ネットワークで繋がる世界

## WAN (Wide Area Network) ネットワーク

WANは、都市や国、さらには大陸を越えてネットワークを接続する広域通信網です。主に海底光ケーブルや長距離光ファイバで構成され、クラウド上のデータセンター同士や国際拠点を結びます。大容量データ転送と高い信頼性が求められ、グローバルなAI処理、クラウドサービス、国際通信の基盤として機能します。

## METROネットワーク

METROネットワークは、都市圏レベルで拠点を相互接続する中間層の通信網です。データセンター、キャリア局舎、地域MECなどを結び、エッジとWANの橋渡し役を担います。低遅延と柔軟なトラフィック制御が特徴で、都市全体の通信需要を効率よく集約・分配する役割を果たします。

## Carrierネットワーク

Carrierネットワークは、通信事業者が構築・運用する通信インフラ全体を指します。基地局、METRO、WAN、データセンターを統合し、通信品質・信頼性・セキュリティを保証します。6G時代には、通信だけでなく計算資源や制御機能も含め、社会インフラとして産業・交通・生活を支える中核となります。

# MECとDCを超高速光ネットワークで接続する光電融合パッケージ

## MEC (Multi-access Edge Computing)

MECは、工場や道路などデータ発生源の近くに設置される分散型の計算基盤です。クラウドに送らず現場でデータ処理を行うことで、通信遅延を最小化し、リアルタイム性が求められる制御や判断を可能にします。

## 超高速光ネットワーク

超高速光ネットワークは、MECとクラウド上のデータセンターを大容量・低遅延で結ぶ基幹インフラです。時間・距離の制約を意識せずに分散システムを統合できるため、産業・交通・都市機能を一体として進化させる基盤となります。

## 6G (第6世代移動通信)

5Gが実現未だに実現できない、エッジの環境を6Gは、超低遅延・超高信頼・超多数接続を同時に実現する事でエッジの自動運転支援や屋外先端現場に対して、センサーが常時ネットワークに接続され、人の操作を介さず協調動作が可能になります。

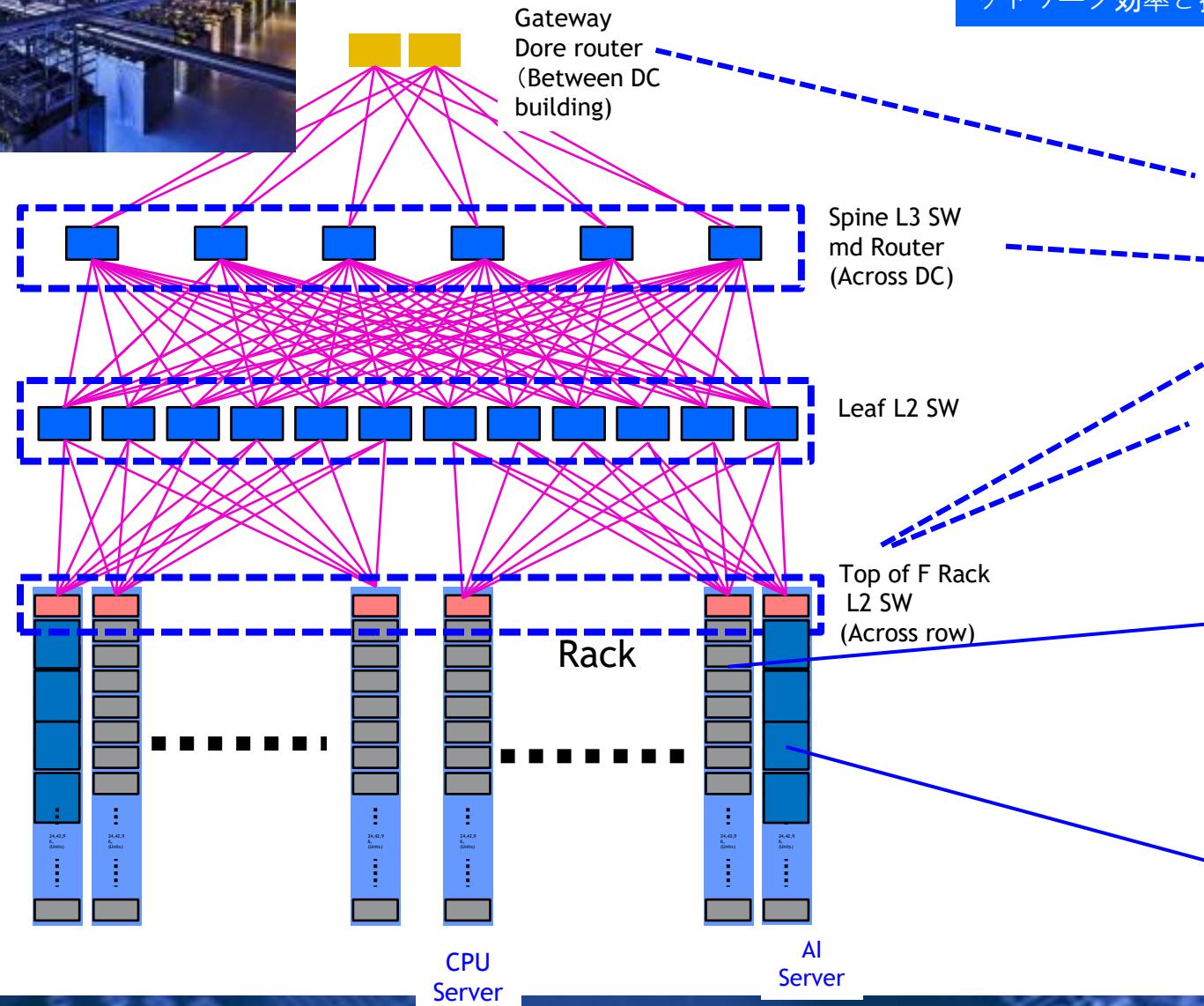

# データコム:クラウドデータセンターにおける 仮想化されたネットワーククロードマップ

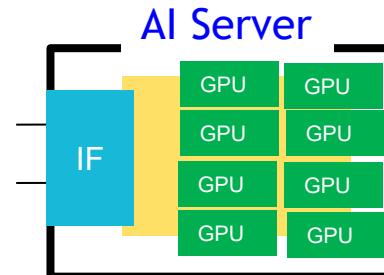

この図はAIサーバー群とCPUサーバーがネットワーク階層を介して接続される構成を示しています。CPUサーバーは1~2ソケット、AIサーバーは4~8ソケット構成で、各サーバーはトップオブラックSWとカッパーウィヤーで接続されます。さらにリーフ、スパインSW間は高速光リンクで接続され、右上の表にEthernet速度が示されています。特に3.2TbE世代からはCPO（コパッケージドオプティクス）の導入が必須とされ、ネットワーク効率と拡張性の飛躍的な向上が求められています。

| Era                 | 100 GbE  | 200 GbE   | 400 GbE   | 800Gb E   | 1.6 TbE    | 3.2 TbE     |

|---------------------|----------|-----------|-----------|-----------|------------|-------------|

| Gateway Core router | 100      | 200       | 400       | 800       | 1600       | 3200        |

| Leaf Spine ToR      | 100      | 200       | 400       | 800       | 1600       | 3200        |

| ToR CPU server      | 25 - 50  | 50 - 100  | 100 - 200 | 200 - 400 | 400 - 800  | 800 - 1600  |

| ToR AI server       | 50 - 100 | 100 - 200 | 200 - 400 | 400 - 800 | 800 - 1600 | 1600 - 3200 |

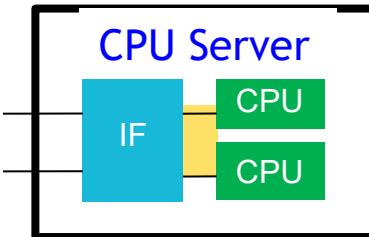

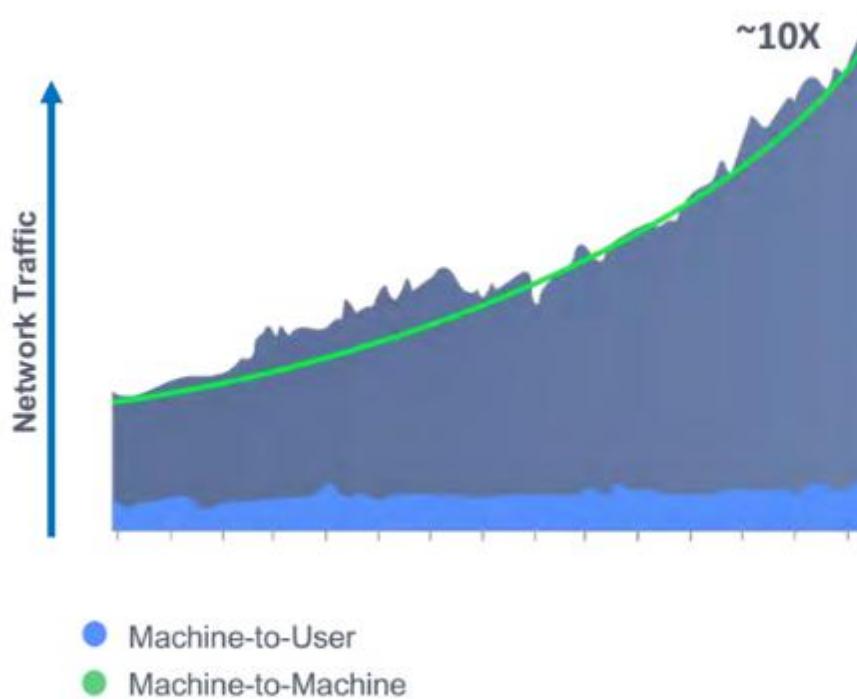

# データセンターにおけるネットワークの消費電力が急増

データセンターのネットワーク消費電力が急増の理由

データセンター内での通信が急増 = サーバー間での通信量が急増 (サーバー間での通信が全体の通信量の85%を超す)

2021年のChatGPTサービス開始による生成AI関連トレーニング・サービスによる加速的な増加

## DC Power Utilization

- Networking is consuming a higher proportion of the data center power budget

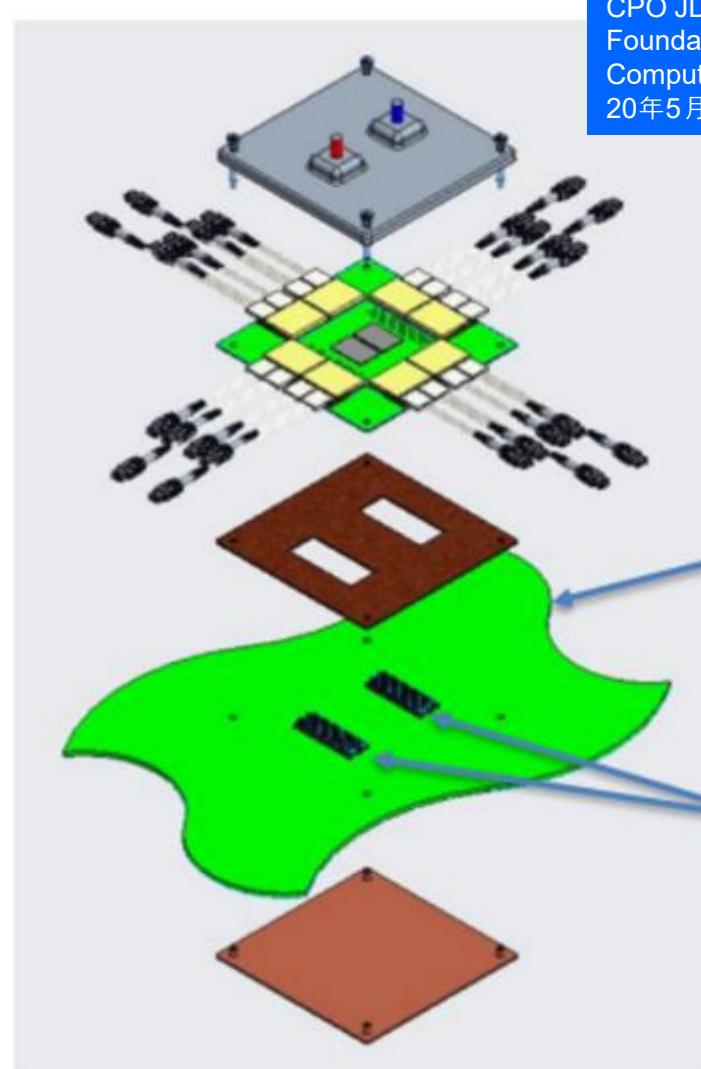

# CPO (Co-Packaged Optics) assembly guide

2022年時点での内容（参考）

2024年OFC: MS, Meta導入見送り(\*1)

CPO JDF(Co-Packaged Optics Joint Development Foundation)はFacebookとMicrosoftがOCP (Open Compute Project)の関係団体として立ち上げた。2020年5月に最初のCo-Packaged仕様書を提出した。

レーザーは現在のInPレーザーでは実情として5年使用が寿命なので、交換可能にする必要があり。発熱源としても高いので、パッケージから外し外部供給を提案している。

<http://docplayer.net/186751965-Co-Packagedd-optic-assembly-guidance-document.html>

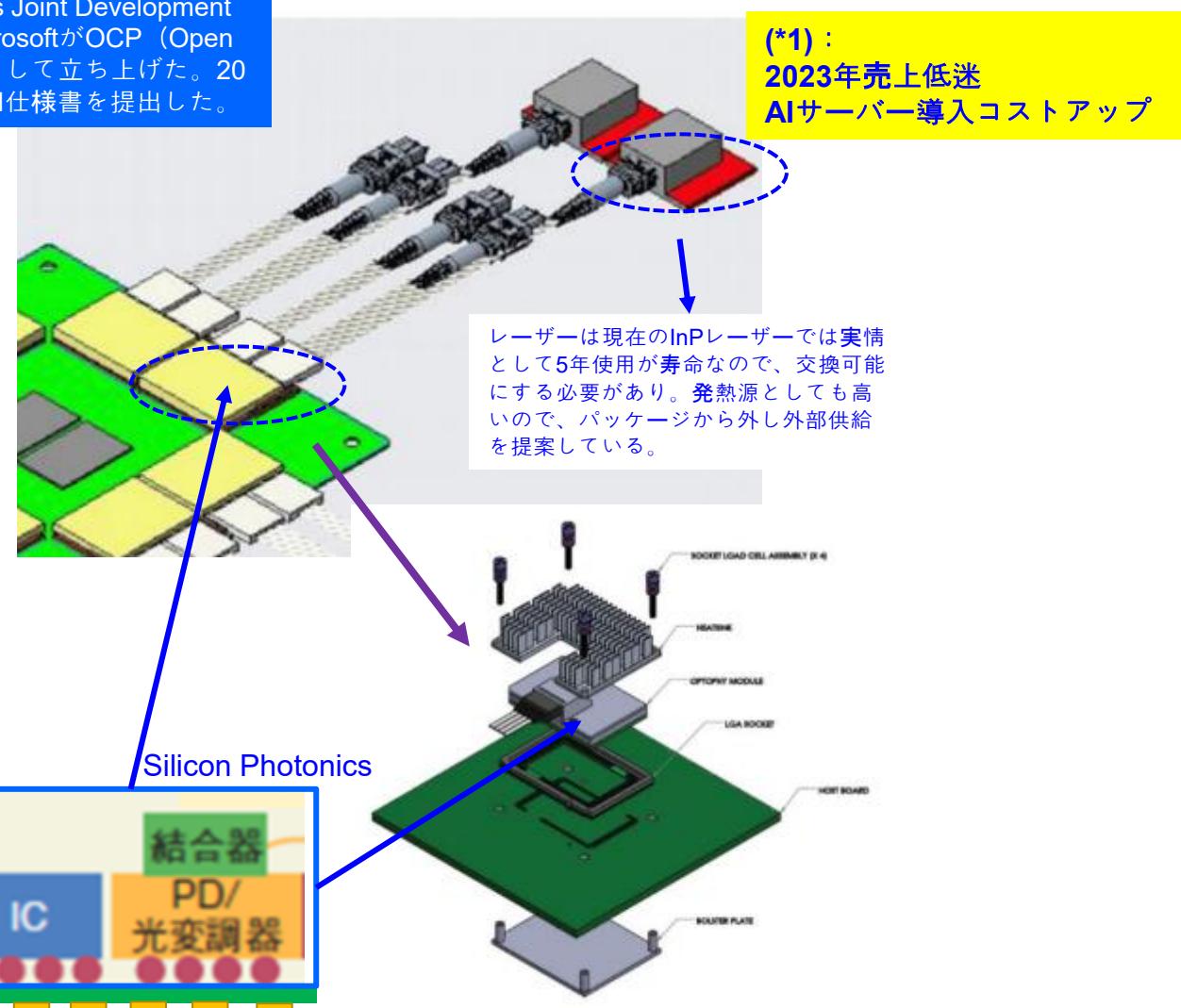

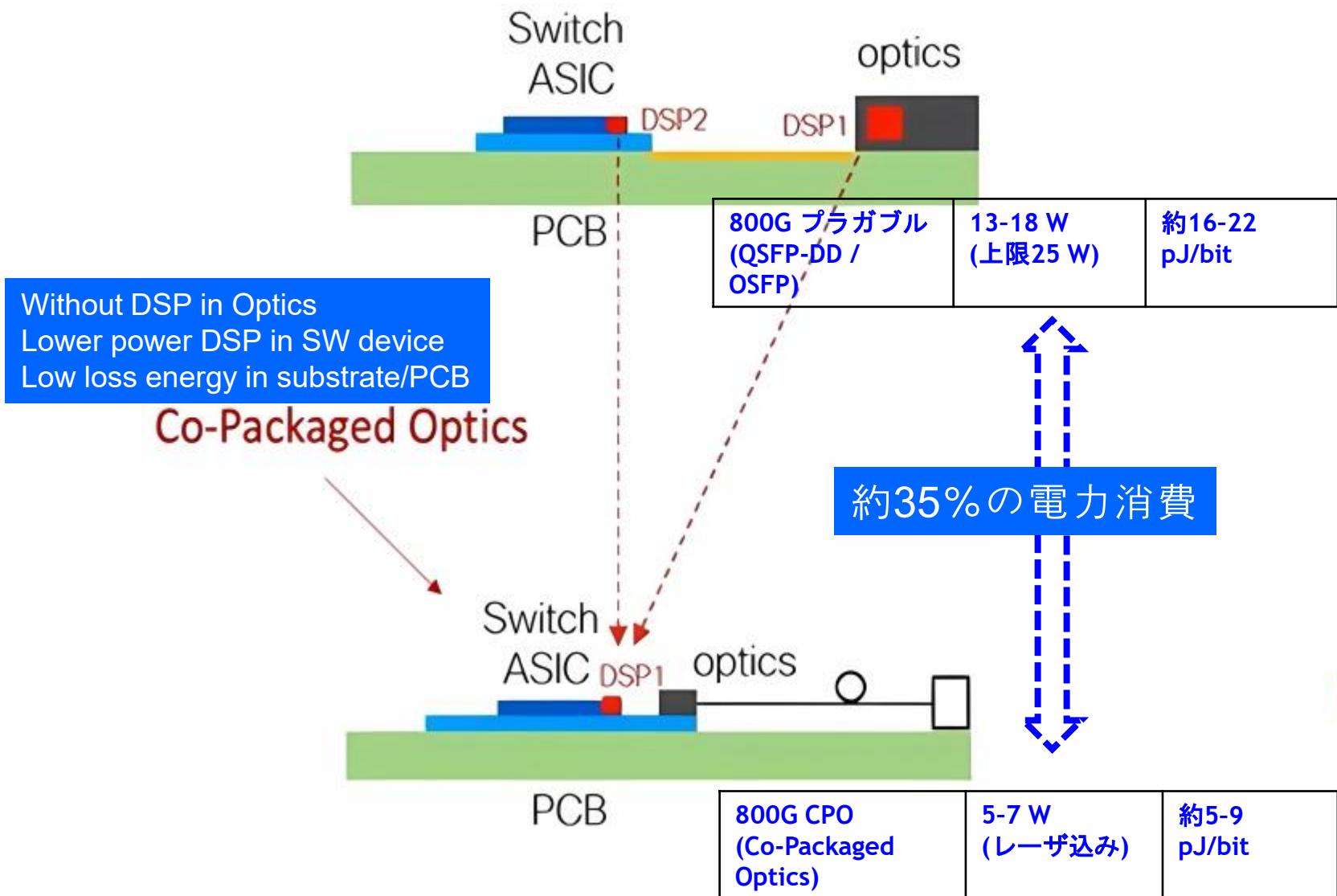

# SW – Pluggable transceiver 信号伝送ロス

[extension://elhekieabhbkpmcefcoobjddigjcaadp/https://docs.broadcom.com/doc/siph-chiplets-in-package-scip](https://docs.broadcom.com/doc/siph-chiplets-in-package-scip)

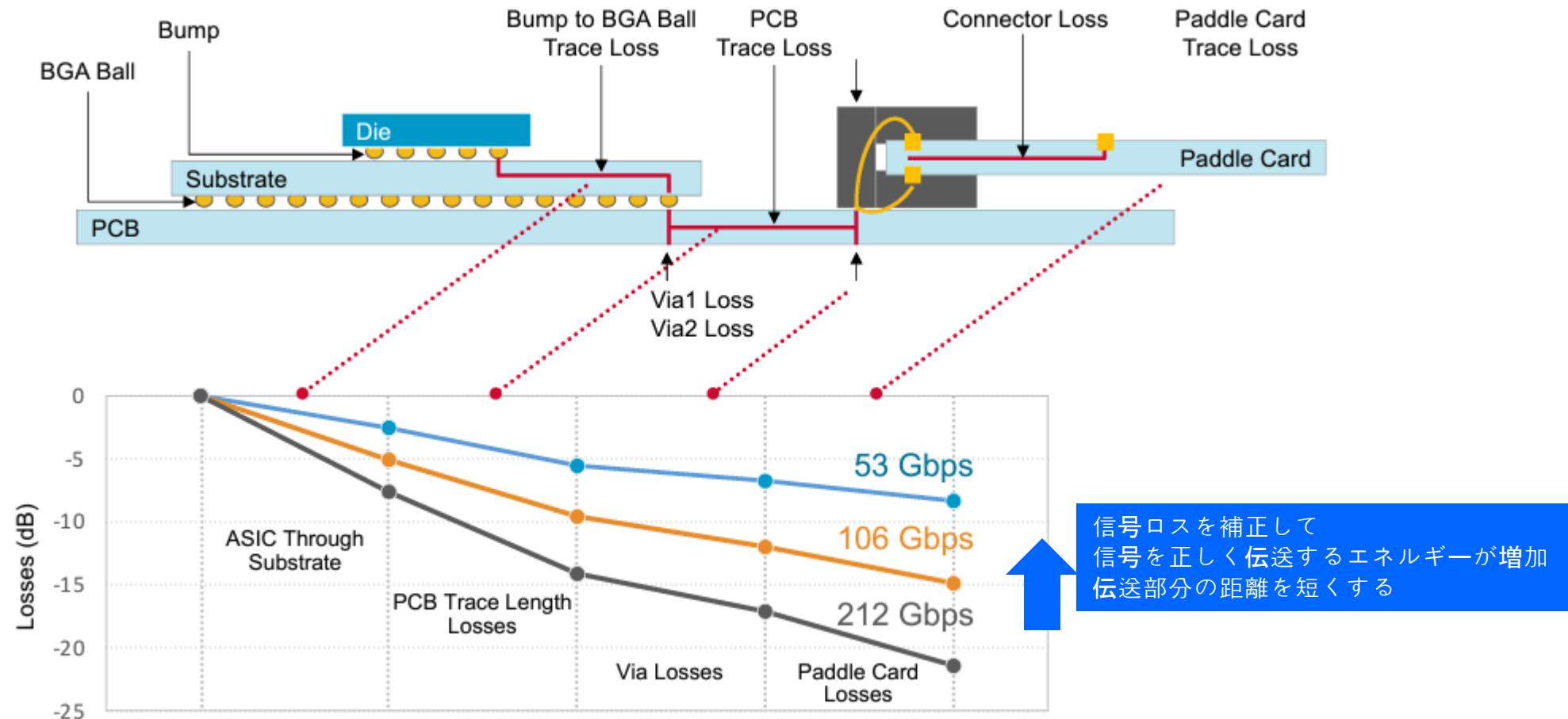

# CPOによる消費エネルギー削減

CPOを導入する事でDSPを省き、光電変換をSilicon Photonicsにする事で大幅なエネルギー削減になる。

<https://community.fs.com/article/lpo-vs-cpo-which-will-dominate-the-data-center-optical-interconnect.html>

2022年OFCにてOIFが示した”回答”として用意したデモ用の試作品

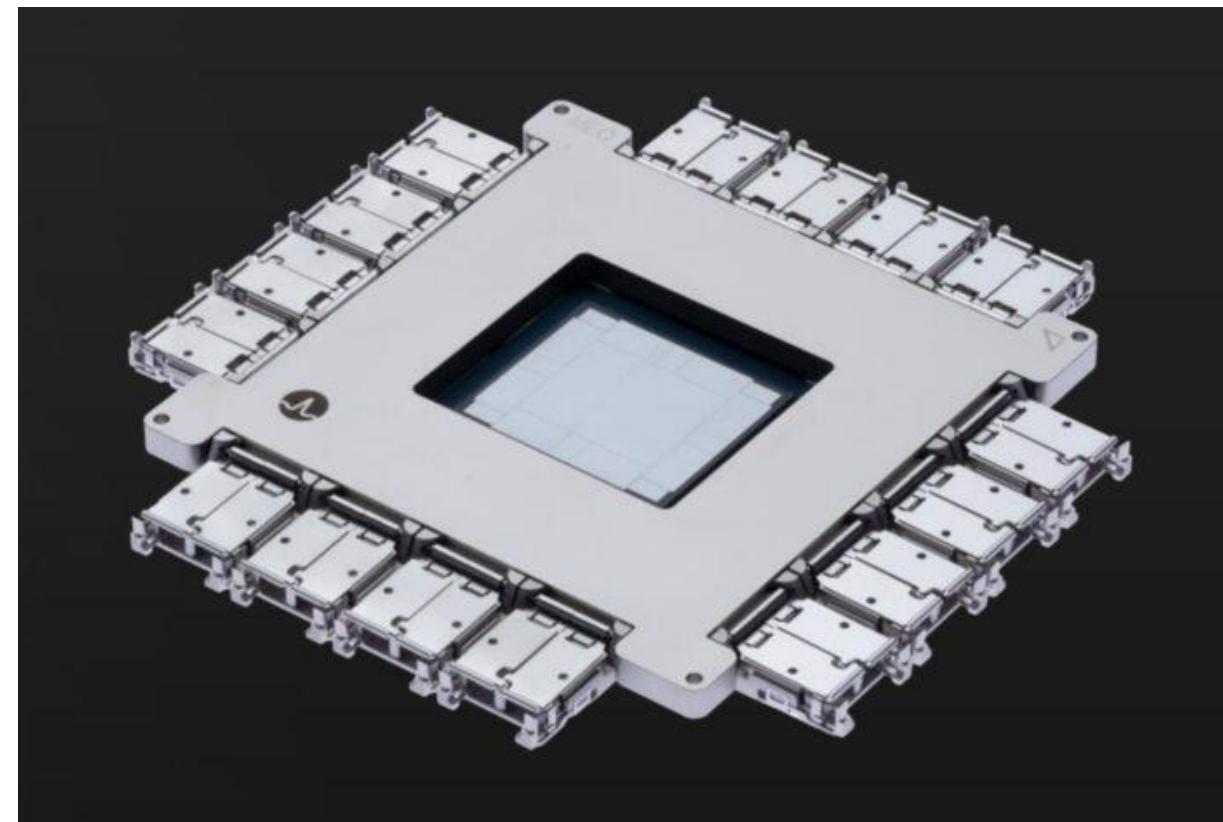

# BroadcomのTomahawk 6 – Davisson 102.4Tスイッチ (Co-Packaged Optics搭載) が出荷開始 (ServeTheHome 2025.10.12掲載)

- CPOスイッチの出荷開始: BroadcomがTomahawk 6 – Davisson (TH6-Davisson) の出荷を発表し、Co-Packaged Optics (CPO) を次世代ネットワーキングに導入

- 性能と光学エンジン: 新しいTH6-Davissonは102.4Tbpsの性能を持ち、Broadcomの6.4Tbps Davisson DR光学エンジンを16個搭載

- 低電力化への貢献: TSMCのCOUPE (Compact Universal Photonic Engine) を活用し、スイッチに必要な消費電力を約70%削減

- SerDesコアの採用: 64個の統合されたCondor 3nm SerDesコアを搭載し、各コアが8個の212.5-Gb/s PAM4 SerDesを集積

- 保守性の向上: 故障率が高い光源部分をプラグイン・交換可能なレーザーモジュールとして分離することで、現場でのサービス (FRU) を可能にする設計を採用

- AIクラスターでの重要性: AIクラスターではネットワーキングの消費電力が課題となっており、CPOによる大幅な低電力化はAIアクセラレータへのリソース配分を最適化する上で大きな利点

- 業界の変革: CPOはスイッチの境界を根本的に書き換えるものであり、業界における次の大きな変化となる

Broadcom TH6 Davisson Cover

出典: <https://www.servethehome.com/broadcom-tomahawk-6-davisson-102-4t-switch-with-co-packaged-optics-shipping/>

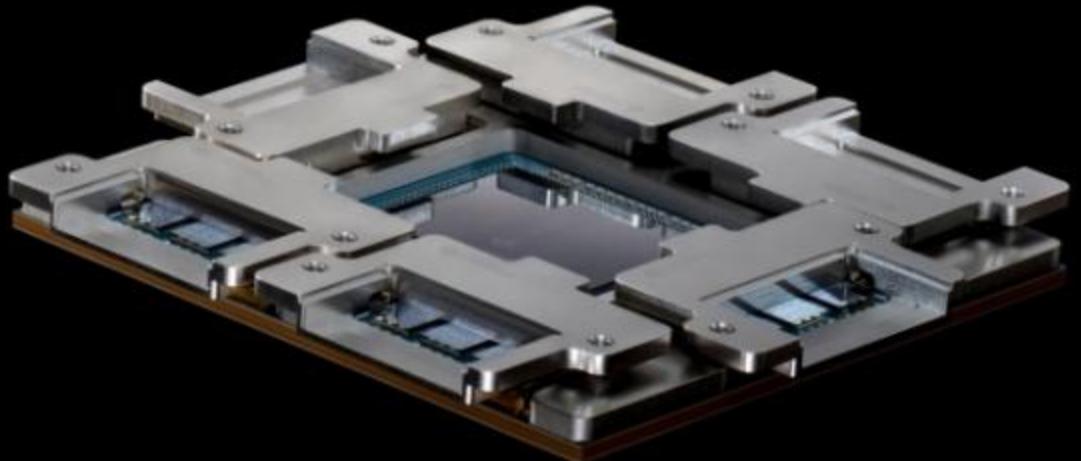

# NVIDIA、AI ファクトリーを数百万の GPU に拡張するCPO SW Spectrum-X Photonics を発表

NVidiaは1.6T製品のクラスター間接続部分のEthernet及びInfiniBandに対してCPOを採用する予定である事をGTC2025で発表。2025年末の導入としている。

NVIDIA Quantum-X フォトニクス: NVIDIA Quantum-X800 InfiniBand プラットフォーム向けの 200G ベースのCo-Packaged Optics

NVIDIA Spectrum-X フォトニクス: NVIDIA Spectrum-X™ Ethernet プラットフォーム向けの 200G ベースのCo-Packaged Optics

出典: [製品ページ: <https://www.nvidia.com/en-us/networking/products/silicon-photonics/>](https://nvidianews.nvidia.com/news/nvidia-spectrum-x-co-packaged-optics-networking-switches-ai-factories)

# TSMC COUPE for Nvidia Spectrum-X and Quantum-X800

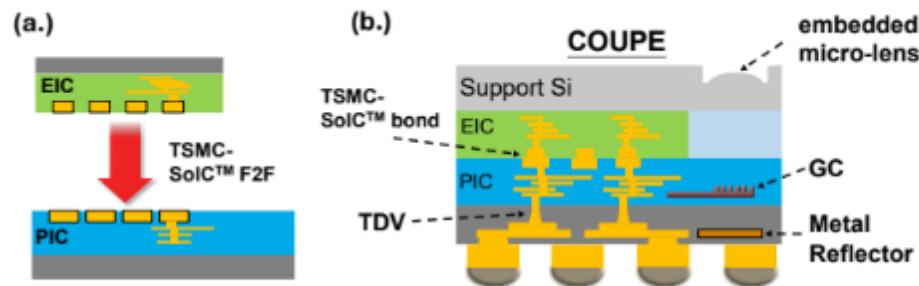

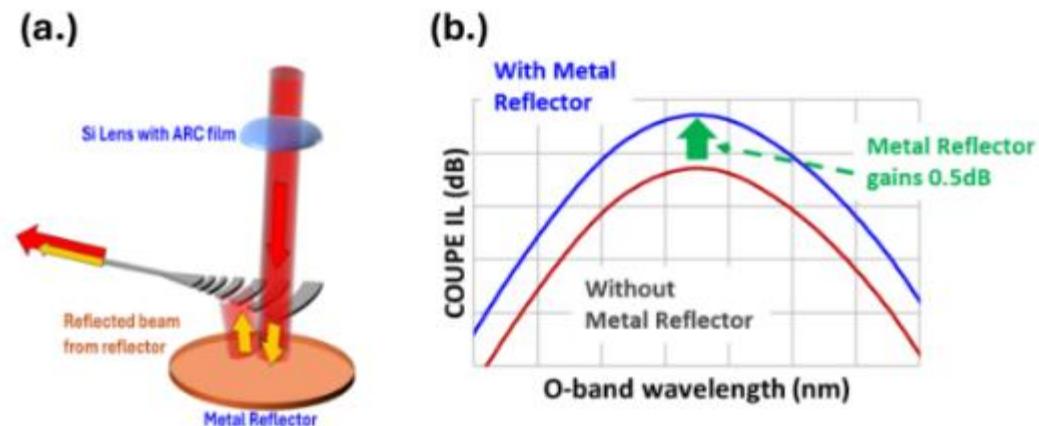

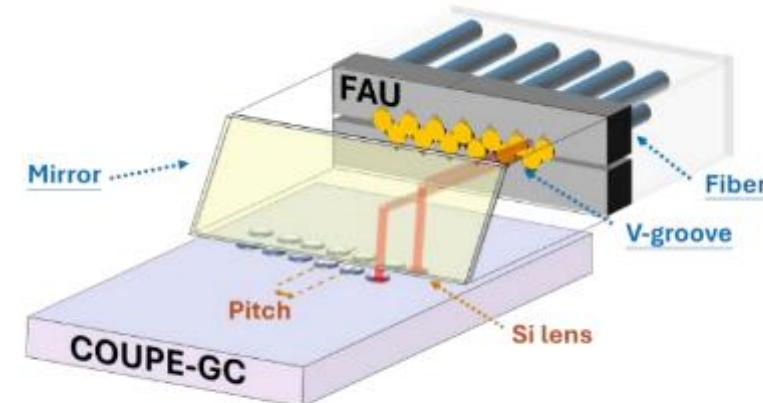

NvidiaのAIスケルアウトように適用されるEthernet SWとInfiniBand SW部分にTSMCの開発してCOUPE (Compact Universal Photonic Engine)が適用される。COUPEの特徴はGratingの光漏れを少なくするためにGrating下に反射板を入れたこと。EICとPCIをHybrid Bondingで接続したこと。

Fig. 2 (a) TSMC-SoIC™ face-to-face (F2F) technology for EIC and PIC bonding. (b) COUPE critical components consist of TSMC-

Fig. 5 (a) The structure of COUPE-GC, with the metal reflector placed beneath the GC. (b) Simulation results indicate the metal reflector provide an 0.5 dB IL gain in COUPE-GC.

Fig. 4 Schematic diagram for COUPE-GC with FAU. The FAU typically includes critical optical components such as the V-groove, mirror, and optical fibers.

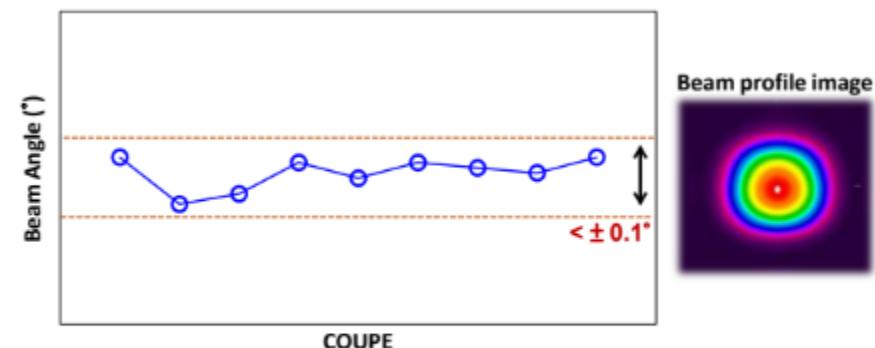

Fig. 8 The variation in the beam angle of COUPE is within  $\pm 0.1^\circ$  along with its profile image.

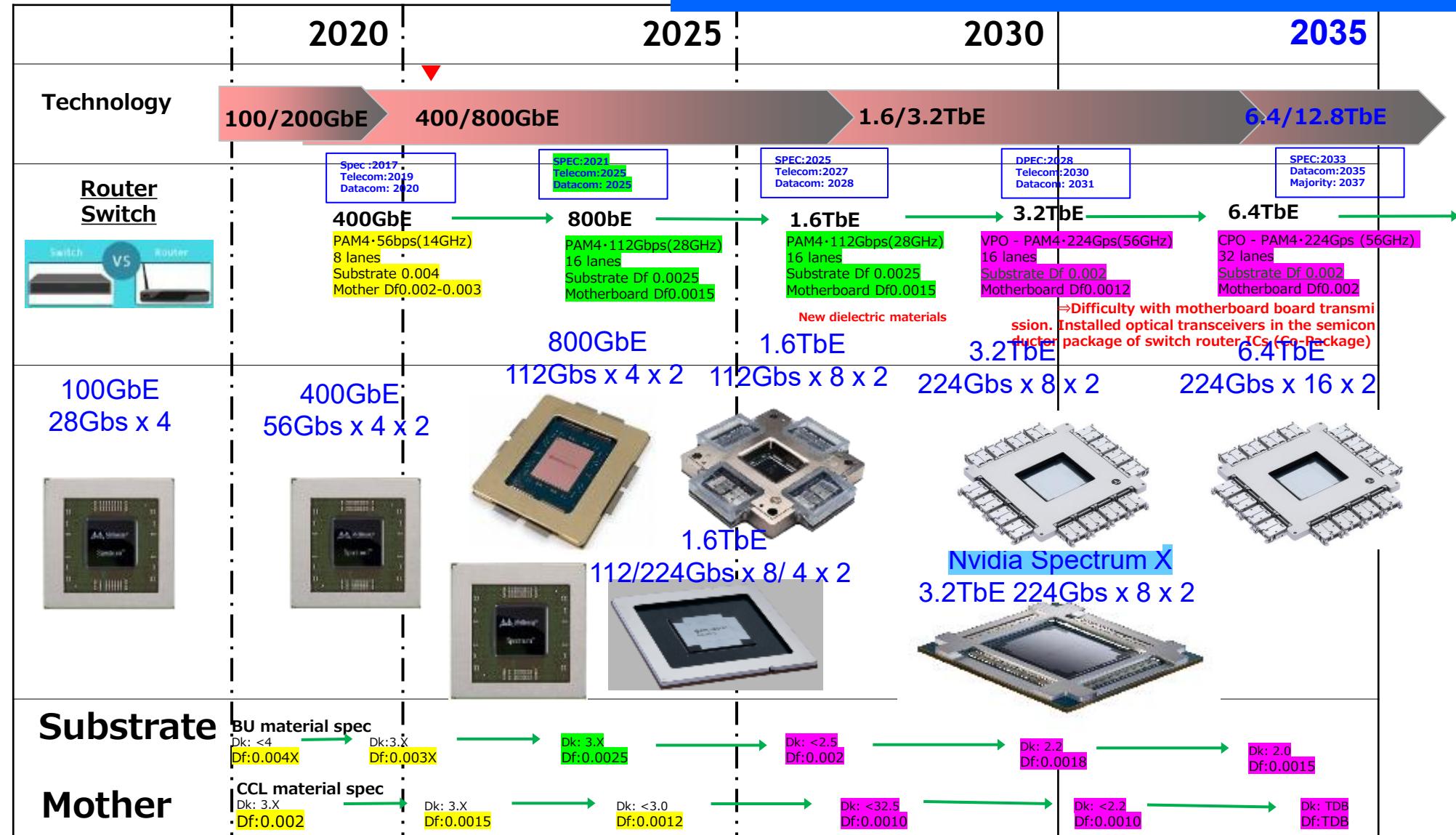

# High speed network ロードマップ – SW

SW製品の3.2TbE世代からCPOは必須になる。Broadcomは800bE世代より中国Tencentと共に市場テストを開始。1.6TbE世代では量産レベルに達した。1.6TbE世代に対してはPluggable用のSWも販売を開始し、112GSerDes適用のPluggable製品はしばらく継続する。

- フィジカルAI x ローカル6G x デジタルツイン

- チッププレットパッケージのトレンド

- 光電融合パッケージのトレンド

- まとめ

## ■ フィジカルAI × ローカル6G × デジタルツイン

- フィジカルAIは、現実空間での即時判断・制御を前提とするAIであり、クラウド集中型処理では遅延と信頼性の限界が顕在化する。ローカル6GとMECは、この制約を克服する分散AI基盤として不可欠である。

- デジタルツインは、現実世界の状態を常時反映し、学習・検証・最適化を担う中核技術である。エッジで取得されたデータをリアルタイムに反映し、制御結果を現場へ即時還流させる循環が価値創出の鍵となる。

- 6Gは単なる高速通信ではなく、分散AIとデジタルツインを結ぶ社会インフラとして位置付けられている。産業、交通、都市分野において、人の介在を最小化した高度な自律システム実装を可能にする基盤技術である。

## ■ チッププレットパッケージのトレンド

- チッププレットは、單一ダイのスケーリング限界を超えるための現実解として定着しており、CPU、GPU、HBM、I/Oを機能単位で分割・再統合する設計が主流となっている。PCIeなどの標準化がその普及を後押ししている。

- AIデータセンターでは、大型インターポーラーを用いた2.5D/3D構造が性能と電力効率の両立に寄与する。一方、MECやエッジ用途では、RDL中心のコンパクトなチッププレット構成が低遅延と信頼性を重視して採用されている。

- 配線密度の向上や基板大型化に伴い、材料・プロセス・信頼性の重要性が増している。絶縁材料、Cu配線、下地基板などの分野で高い競争力を持つ日本企業にとって、チッププレット時代は大きな事業機会となる。

## ■ 光電融合パッケージ（CPO）のトレンド

- ネットワーク帯域の急拡大により、データセンターではネットワーク消費電力が新たなボトルネックとなっている。従来のプラガブル光モジュールでは、DSPと長距離電気配線が電力増加の主要因となっている。

- CPOは光エンジンをスイッチASIC近傍に配置することで電気配線を短縮し、DSPを削減する。800G世代では消費電力を約35%低減し、pJ/bitレベルでのエネルギー効率改善が可能となる点が大きな特徴である。

- 一方で、冷却、保守性、レーザー寿命といった課題も存在する。CPOは単なる光モジュール置換ではなく、パッケージ、材料、冷却を含めたシステム全体最適化技術として捉える必要がある。

# SBR Technology

ご清聴ありがとうございました

ご質問をどうぞ…